PCB走线上的传播延迟是信号在该走线上传播所需的单向(从源到负载)时间。用单位长度的时间表示。传播延迟是介电常数(Er)和走线几何形状/结构的函数。对于给定的PCB层压板和给定的介电常数,对于各种阻抗线,时间延迟是固定的。

为什么会发生传播延迟?

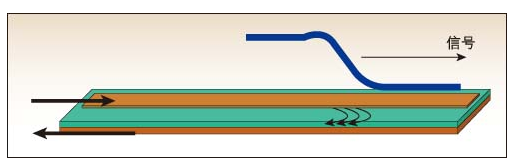

杂散电容是任何电路中的时间延迟的原因。我们并非故意在电路中使用电容器;仍然有电容。总电容取决于其相对尺寸和走线几何形状。杂散电容包括走线之间的电容,走线与相邻接地平面之间以及走线与自由空间之间的电容。 杂散电容的影响导致信号延迟。最重要的是,当数字信号改变状态时,由于必须对杂散电容进行充电/放电,因此需要花费一些时间在目标位置进行转换。

传输延迟和传播延迟之间有什么区别?

传输延迟和传播延迟可以互换使用,但是当需要在模拟/数字方面对系统进行分析时,需要对它们进行不同的处理。可以通过以下传输线方法来计算遍及PCB走线的逻辑信号时序:

方法1:当PCB走线的一侧时间延迟等于或大于所施加信号的上升/下降时间的一半时,以其特性阻抗端接传输线。

示例:Er为4的2英寸微带线会出现大约270ps的延迟。使用上述方法,只要信号上升时间小于500ps,端接将是准确的。

方法2:使用2英寸PCB轨道长度/纳秒(上升/下降时间)方法。如果信号走线超过走线长度标准,则必须使用端接。

示例:如果轨道长度等于或大于10英寸,则应使用其特征阻抗来终止为上升/下降时间为5ns的高速逻辑而设计的PCB轨道。

评论列表